TSMC and Cadence Collaborate to Deliver AI-Driven Advanced-Node Design Flows, Silicon-Proven IP and 3D-IC Solutions

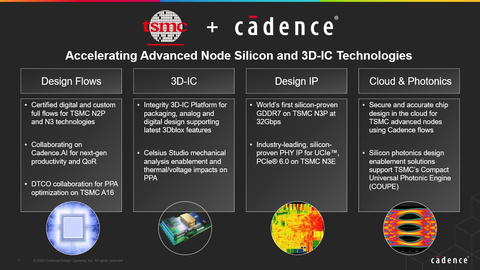

Cadence Design Systems (NASDAQ: CDNS) and TSMC are collaborating to enhance productivity and optimize performance for AI-driven advanced-node designs and 3D-ICs. Key highlights include:

1. AI-driven digital and custom design flows for TSMC's N2P and N3 technologies

2. Collaboration on A16 design solutions to optimize power, performance, and area (PPA)

3. Cadence Integrity 3D-IC Platform supporting latest 3Dblox features

4. Celsius Studio mechanical analysis enablement for TSMC 3DFabric

5. Silicon-proven GDDR7 IP running at 32Gbps on TSMC N3 technology

6. Support for secure chip design in the cloud and TSMC silicon photonics technologies

The partnership aims to accelerate time to market and increase performance for advanced silicon solutions capable of handling large datasets and computations required by AI applications.

Cadence Design Systems (NASDAQ: CDNS) e TSMC stanno collaborando per migliorare la produttività e ottimizzare le prestazioni per design avanzati in nodo AI e 3D-IC. I punti salienti includono:

1. Flussi di design digitali e personalizzati guidati dall'AI per le tecnologie N2P e N3 di TSMC

2. Collaborazione su soluzioni di design A16 per ottimizzare potenza, prestazioni e area (PPA)

3. Piattaforma Cadence Integrity 3D-IC che supporta le ultime funzionalità di 3Dblox

4. Abilitazione dell'analisi meccanica di Celsius Studio per TSMC 3DFabric

5. IP GDDR7 dimostrato in silicio che funziona a 32Gbps sulla tecnologia N3 di TSMC

6. Supporto per design di chip sicuri nel cloud e tecnologie fotoniche in silicio di TSMC

La partnership mira ad accelerare il tempo di immissione sul mercato e aumentare le prestazioni per soluzioni avanzate in silicio in grado di gestire grandi volumi di dati e calcoli richiesti dalle applicazioni AI.

Cadence Design Systems (NASDAQ: CDNS) y TSMC están colaborando para mejorar la productividad y optimizar el rendimiento para diseños avanzados impulsados por IA y 3D-ICs. Los aspectos más destacados incluyen:

1. Flujos de diseño digital y personalizado impulsados por IA para las tecnologías N2P y N3 de TSMC

2. Colaboración en soluciones de diseño A16 para optimizar potencia, rendimiento y área (PPA)

3. Plataforma Cadence Integrity 3D-IC que soporta las últimas características de 3Dblox

4. Habilitación del análisis mecánico en Celsius Studio para TSMC 3DFabric

5. IP GDDR7 probado en silicio funcionando a 32Gbps en la tecnología N3 de TSMC

6. Soporte para diseño seguro de chips en la nube y tecnologías de fotónica de silicio de TSMC

La asociación tiene como objetivo acelerar el tiempo de comercialización y aumentar el rendimiento de soluciones avanzadas de silicio capaces de manejar grandes conjuntos de datos y cálculos requeridos por aplicaciones de IA.

Cadence Design Systems (NASDAQ: CDNS)와 TSMC는 AI 기반 최첨단 설계 및 3D-IC의 생산성을 향상하고 성능을 최적화하기 위해 협력하고 있습니다. 주요 내용은 다음과 같습니다:

1. TSMC의 N2P 및 N3 기술을 위한 AI 기반 디지털 및 맞춤형 설계 흐름

2. 전력, 성능 및 면적(PPA)을 최적화하기 위한 A16 설계 솔루션 협력

3. 최신 3Dblox 기능을 지원하는 Cadence Integrity 3D-IC 플랫폼

4. TSMC 3DFabric을 위한 Celsius Studio 기계 분석 활성화

5. TSMC N3 기술에서 32Gbps로 작동하는 검증된 GDDR7 IP

6. 클라우드에서의 안전한 칩 설계 및 TSMC 실리콘 광자 기술 지원

이번 파트너십은 시장 출시 시간을 단축하고 AI 애플리케이션에 필요한 대량의 데이터 및 계산을 처리할 수 있는 고급 실리콘 솔루션의 성능을 높이는 것을 목표로 하고 있습니다.

Cadence Design Systems (NASDAQ: CDNS) et TSMC collaborent pour améliorer la productivité et optimiser les performances des conceptions avancées pilotées par l'IA et des 3D-IC. Les points clés incluent :

1. Flux de conception numériques et personnalisés pilotés par l'IA pour les technologies N2P et N3 de TSMC

2. Collaboration sur des solutions de conception A16 pour optimiser la puissance, les performances et la surface (PPA)

3. Plateforme Cadence Integrity 3D-IC prenant en charge les dernières fonctionnalités de 3Dblox

4. Activation de l'analyse mécanique de Celsius Studio pour le TSMC 3DFabric

5. IP GDDR7 éprouvé en silicium fonctionnant à 32Gbps sur la technologie N3 de TSMC

6. Soutien à la conception de puces sécurisées dans le cloud et aux technologies de photonique en silicium de TSMC

Ce partenariat vise à accélérer le temps de mise sur le marché et à augmenter les performances des solutions silicium avancées capables de gérer de grands ensembles de données et des calculs nécessaires aux applications d'IA.

Cadence Design Systems (NASDAQ: CDNS) und TSMC arbeiten zusammen, um die Produktivität zu steigern und die Leistung für KI-gesteuerte Designs in fortgeschrittenen Knoten und 3D-ICs zu optimieren. Zu den wichtigsten Highlights gehören:

1. KI-gesteuerte digitale und kundenspezifische Designabläufe für die N2P- und N3-Technologien von TSMC

2. Zusammenarbeit an A16-Designlösungen zur Optimierung von Leistung, Effizienz und Fläche (PPA)

3. Cadence Integrity 3D-IC-Plattform, die die neuesten 3Dblox-Funktionen unterstützt

4. Celsius Studio mechanische Analyseaktivierung für TSMC 3DFabric

5. Siliziumbewährte GDDR7-IP, die mit 32Gbps auf der TSMC N3-Technologie läuft

6. Unterstützung für sicheres Chipdesign in der Cloud und TSMC Siliziumphotonik-Technologien

Die Partnerschaft zielt darauf ab, die Markteinführungszeit zu beschleunigen und die Leistung von fortschrittlichen Siliziumlösungen zu erhöhen, die große Datenmengen und Berechnungen bewältigen müssen, die von KI-Anwendungen erforderlich sind.

- Collaboration with TSMC on advanced N2P and N3 technologies

- AI-driven design flows to enhance productivity and optimize performance

- Support for 3D-IC design with Cadence Integrity 3D-IC Platform

- First silicon-proven GDDR7 IP running at 32Gbps on TSMC N3 technology

- Enablement of secure chip design in the cloud for TSMC's advanced process nodes

- None.

Insights

This collaboration between TSMC and Cadence represents a significant advancement in semiconductor design and manufacturing capabilities, particularly for AI applications. Key points include:

- AI-driven design flows for TSMC's advanced N2P and N3 nodes, which will enable more efficient chip designs for AI workloads

- Collaboration on A16 design solutions to optimize power, performance and area (PPA)

- Advancements in 3D-IC technology, including the Integrity 3D-IC Platform and 3Dblox features, which allow for more complex chip designs

- Development of critical IP like the first silicon-proven GDDR7 IP at 32Gbps on TSMC N3, essential for high-performance AI systems

- Support for silicon photonics and automotive applications, expanding the reach of these advanced technologies

This partnership is likely to accelerate the development of more powerful and efficient AI chips, potentially impacting the entire semiconductor industry and AI hardware landscape.

The collaboration between TSMC and Cadence is strategically significant for both companies and the broader semiconductor industry. For Cadence (CDNS), this partnership:

- Strengthens its position in the rapidly growing AI chip design market

- Enhances its product offerings, potentially driving increased software sales and market share

- Aligns the company with TSMC, the world's largest contract chipmaker, providing a competitive edge

Financially, this could translate to:

- Increased revenue from software licenses and IP sales

- Potential for higher margins as AI-driven solutions often command premium pricing

- Long-term growth prospects as demand for AI chips continues to surge

Investors should watch for increased adoption of Cadence's AI-driven design tools and any impact on the company's financial performance in upcoming quarters.

This collaboration signifies a major shift in the semiconductor industry towards AI-optimized chip design and manufacturing. Market implications include:

- Accelerated development of AI chips, potentially leading to faster market penetration of AI technologies across various sectors

- Increased competition in the EDA (Electronic Design Automation) space, as other players may seek similar partnerships

- Potential for new market entrants in AI hardware, enabled by more accessible advanced chip design capabilities

- Growth in the 3D-IC and advanced packaging markets, as these technologies become more mainstream

The partnership could also influence the broader tech ecosystem, affecting companies in cloud computing, data centers and AI software development. Long-term, this could lead to more powerful AI systems, potentially disrupting various industries and creating new market opportunities.

Highlights:

- AI-driven digital and custom design flows available for the latest TSMC N2P and N3 technologies

- Cadence is collaborating with TSMC on A16 design solutions to optimize PPA

- Cadence Integrity 3D-IC Platform unifying packaging, analog and digital design supports latest 3Dblox features

- Collaboration includes Celsius Studio mechanical analysis enablement and thermal/voltage impacts on power/IR/STA and what-if in-design analysis

- Design IP powers the AI factory, including the industry’s first silicon-proven GDDR7 IP running at 32Gbps on the TSMC N3 technology

- Cadence solutions support secure chip design in the cloud, with design solutions to support TSMC silicon photonics technologies

Cadence is collaborating with TSMC to enhance productivity and optimize product performance for AI-driven advanced-node designs and 3D-ICs. The rapid adoption of AI applications has created unprecedented demand for advanced silicon solutions capable of handling colossal datasets and computations. TSMC and Cadence are together empowering customers to accelerate time to market while increasing performance. (Graphic: Business Wire)

TSMC has certified �䲹���Գ���’s industry-leading and design flows for implementation and signoff on TSMC’s latest N3 and N2P process technologies. As long-standing design technology co-optimization (DTCO) partners, TSMC and Cadence continue that tradition by collaborating to optimize power, performance and area (PPA) on A16, adding EDA features to enable advanced features such as backside routing.

Cadence and TSMC are also collaborating on to drive next-generation digital and analog design automation fueled by AI, delivering industry-leading productivity and quality of results. Cadence.AI is a chips-to-systems AI platform spanning all aspects of design and verification. The collaboration between TSMC and Cadence is focused on three main domains:

- The Cadence® Cerebrus™ Intelligent Chip Explorer applies AI to digital design for converging on the optimal PPA.

- The uses generative AI for design debug and analytics, helping with PPA analysis.

-

�䲹���Գ���’s Virtuoso® Studio enables migrating legacy custom and analog designs to modern nodes and performs circuit optimization and high-sigma

Monte Carlo analysis.

The Cadence Integrity™ 3D-IC Platform is a leading system-level exploration solution and a single-vendor platform that unifies packaging, analog and digital implementation—making efficient 3D-IC design possible. This opens new opportunities for innovation by supporting all the latest 3Dblox features and constructs. To enable the ultra-high-density interconnect in TSMC 3DFabric™ technologies, TSMC and Cadence are collaborating on a next-generation high-capacity substrate router for die-to-die and die-to-substrate connections.

Multiphysics analyses and optimization is a critical dimension of success for 3D-IC technologies. TSMC and Cadence are collaborating to enable warpage/stress analysis for TSMC 3DFabric in addition to electrical/thermal analysis, and �䲹���Գ���’s Celsius™ Studio warpage/stress analysis simulation results have been validated. Thermal and voltage impacts on power/IR/STA are also enabled and verified inside the Cadence Integrity 3D-IC Platform for TSMC 3DFabric.

The AI factories’ insatiable appetite for data is increasing the requirements for interconnects and pushing power envelopes. Cadence has a for efficiently moving data between chiplets and across data centers, including Universal Chiplet Interconnect Express™ (UCIe™) 1.0, PCI Express® (PCIe®) 6.0 and the world’s first silicon-proven GDDR7 on TSMC N3, running at 32Gbps, which provides the best price/performance for AI interfaces in both data centers and network edges. To address the growing communication challenges between these chips, Cadence silicon photonics design enablement solutions support TSMC’s Compact Universal Photonic Engine (COUPE).

TSMC and Cadence are jointly collaborating with the leaders in the automotive space. As the silicon content in today’s automotive designs continues to grow, IP development for current and future process nodes, such as TSMC N5A and later N3A, is even more critical.

TSMC and Cadence have also collaborated to showcase the accuracy and scalability offered by �䲹���Գ���’s front-to-backend chip design flows on the Cloud for TSMC’s advanced process nodes. Through this collaboration, mutual customers can shorten design schedules by adopting �䲹���Գ���’s wide range of .

“TSMC and Cadence have a long-standing, successful partnership that turns the world’s designs into silicon reality,” said Chin-Chi Teng, senior vice president and general manager of the Digital & Signoff Group at Cadence. “Together, we are revolutionizing the future of silicon design with AI-powered EDA software, enabled for TSMC’s latest process technologies. Our ongoing collaboration on innovative solutions for next-generation technologies like TSMC A16 and 3Dblox is paving the way for the AI factories of tomorrow.”

“In collaboration with Cadence, we’ve successfully enabled AI-optimized design flows for TSMC’s N2 technology and are driving advancements in 3D-IC design,” said Dan Kochpatcharin, head of Ecosystem and Alliance Management Division at TSMC. “This marks a significant leap forward in digital and custom solutions, paving the way for the technology innovations that will power the AI infrastructure.”

About Cadence

Cadence is a pivotal leader in electronic systems design, building upon more than 30 years of computational software expertise. The company applies its underlying Intelligent System Design strategy to deliver software, hardware and IP that turn design concepts into reality. Cadence customers are the world’s most innovative companies, delivering extraordinary electronic products from chips to boards to complete systems for the most dynamic market applications, including hyperscale computing, 5G communications, automotive, mobile, aerospace, consumer, industrial and healthcare. For 10 years in a row, Fortune magazine has named Cadence one of the 100 Best Companies to Work For. Learn more at .

© 2024 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo and the other Cadence marks found at are trademarks or registered trademarks of Cadence Design Systems, Inc. UCIe Consortium, Universal Chiplet Interconnect Express and UCIe are trademarks of the UCIe Consortium. PCI Express and PCIe are registered trademarks of PCI-SIG. All other trademarks are the property of their respective owners.

Category: Featured

View source version on businesswire.com:

Cadence Newsroom

408-944-7039

newsroom@cadence.com

Source: Cadence Design Systems, Inc.

FAQ

What are the key technologies Cadence and TSMC are collaborating on for AI-driven designs?

What is the significance of Cadence's silicon-proven GDDR7 IP for CDNS stock?

How is Cadence (CDNS) supporting TSMC's advanced process nodes in the cloud?